SPI

SPI(Serial Peripheral Interface)는 주변 장치와 직렬로 통신하기 위한 인터페이스 입니다. 주로 근거리에서 칩(IC)과 칩 사이에 통신을 위해서 사용합니다.

클럭

SPI는 지난 글에서 GPIO를 이용하여 FND 모듈을 제어한 것과 같이 클럭 주기에 맞춰서 데이터를 송수신합니다. UART와는 다르게 통신 속도를 지정하지 않고, 클럭을 사용하기 때문에 속도 제한이 없습니다.

SPI의 클럭 위상(CPHA, Clock Phase)은 1 Edge와 2 Edge로 나뉩니다. 클럭의 극성(CPOL, Clock Polarity)이 HIGH인 경우 1 Edge에서는 클럭이 하강하는 시점의 MOSI/MISO 상태를 확인하고, 2 Edge에서는 클럭이 상승하는 시점에 MOSI/MISO 상태를 확인합니다.

CPOL이 LOW인 경우에는 반대로 1 Edge에서 상승하는 시점에, 2 Edge에서는 하상하는 시점에 MOSI/MISO를 확인합니다.

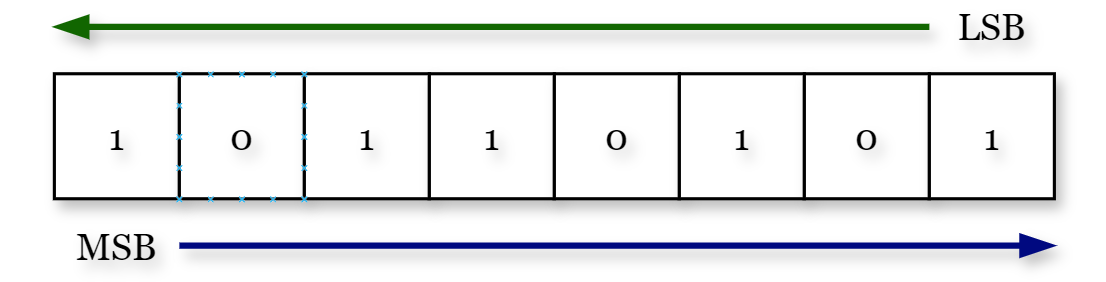

MSB와 LSB

SPI는 데이터를 전송하는 순서에 따라 MSB와 LSB로 나뉩니다. MSB(Most Significant Bit)는 최상위 비트부터 데이터를 전송하는 방식이고, LSB(Lesat Significant Bit)는 최하위 비트부터 데이터를 전송하는 방식입니다.

Full Duplex

| 전이중(Full Duplex) | 반이중(Half Duplex) | 단방향(Simplex) | |

| 방향 | 양방향 | 쌍방향 | 단방향 |

| 설명 | 송신과 수신 동시에 가능 | 송신과 수신 동시에 불가능 | 송신만 혹은 수신만 가능 |

| 예시 | 휴대전화 | 무전기 | 진동벨 |

SPI는 전이중(Full Duplex) 통신이 가능합니다. 전이중 통신이란 송신하는 동시에 수신이 가능하다는 것입니다. 반이중(Half Duplex)은 송신과 수신이 모두 가능하지만 한번에 하나의 동작만 가능하고, 단방향(Simplex) 방식은 송신이나 수신 하나의 동작만 하는 것을 의미합니다. SPI는 세 가지 방식 모두 사용이 가능합니다.

1:1 연결

SPI는 기본적으로 4개의 핀을 사용합니다. SCLK은 데이터를 전송하는 기준이 되는 클럭을 의미합니다. 클럭 신호를 보내는 칩을 마스터, 클럭 신호를 받는 칩을 슬레이브라고 합니다. MOSI는 Master Out Slave In의 약자로 마스터에서 데이터를 전송할 때 사용하는 핀이고, MISO는 반대로 슬레이브에서 데이터를 전송할 떄 사용하는 핀입니다. SS는 Slave Select의 약자로 하나의 마스터에 여러개의 슬레이브가 연결되어 있을 때 슬레이브를 선택하기 위해 사용합니다.

SS는 CS(Chip Select)라고 부르기도 합니다.

SPI는 SCLK와 MOSI만 사용하여 단방향으로 통신하거나, SCLK, DIO(MOSI/MISO)를 사용해서 반이중으로 통신하는 등 통신 방향에 따라 핀을 유동적으로 구성할 수 있습니다.

1:N 연결

SPI 다중 연결을 하기 위해서는 위 사진처럼 SCLK, MOSI, MISO 핀을 모든 슬레이브에 연결하고, SS 핀만 각 슬레이브에 따로 연결해야 합니다. SS 1~3 핀을 사용하여 원하는 슬레이브만 선택하여 데이터를 송신할 수 있습니다. 다만 슬레이브가 늘어날수록 SS 핀을 추가해야한다는 단점이 있습니다.

이번에는 지난 글에서 GPIO로 제어했던 FND 모듈을 SPI 방식으로 제어합니다.

개발환경

개발도구

| 구분 | 내용 |

| 통합 개발 환경 | STM32CubeIDE |

BOM

| 상품명(링크) | 수량 |

| STM32F103 Development Board | 1 |

| 74HC595D FND 모듈 | 1 |

| ST-Link STM32 디버거 (with JTAG 20-pin cable) | 1 |

| USB 2.0 A to mini-B 커넥터 | 1 |

| 소켓 점퍼 케이블 40P (칼라) (M/M) 20cm | 5 |

H/W

H/W 구성도

HSI(Human System Interface)

강의에서는 CPHA를 1 Edge로 사용하지만, 제가 가지고 있는 FND 모듈의 칩과 CPOL이 달라서 2 Edge로 설정해야합니다. 해당 부분은 아래에서 추가로 설명하겠습니다.

S/W

소스코드

// ...

static SPI_HandleTypeDef *mhspi;

void init_fnd(SPI_HandleTypeDef *hspi)

{

mhspi = hspi;

_LED_0F[0] = 0xC0; //0

_LED_0F[1] = 0xF9; //1

_LED_0F[2] = 0xA4; //2

// ...

}

void send(uint8_t x)

{

HAL_SPI_Transmit(mhspi, &x, 1, 100);

}

// ...

트러블슈팅

문제: SPI 방식으로 변경시 출력값 오류

GPIO 방식으로 FND 모듈을 제어했을 때는 출력이 잘 나왔는데, SPI 방식으로 변경 후 갑자기 출력이 이상하게 나오는 현상이 발생했습니다. 다른 숫자가 출력되는 것이 아니라 아예 전혀 다른 세그먼트와 비트가 점등되었기 때문에 하드웨어 설정 부분에 문제가 있을 것이라고 예상했고, CPOL과 CPHA 설정을 변경하면서 테스트를 해봤습니다.

| HIGH | LOW | |

| 1 Edge | 비정상 | 정상 |

| 2 Edge | 정상 | 정상 |

테스트 결과 CPOL이 HIGH이고 CPHA가 1 Edge인 경우에만 비정상적인 출력이 나온다는 것을 알게 되었습니다.

원인: Clock Polarity 차이로 인한 비트 누락

CPOL과 CPHA에 따라 출력 문제가 생기는 원인을 찾기 위해 먼저 제가 가지고 있는 FND 모듈의 Nexperia - 74HC595D 칩의 데이터시트를 확인해봤습니다. SCLK에 해당하는 SHCP의 CPOL은 LOW이고 CPHA는 1 Edge인 것을 볼 수 있습니다.

강의에서 사용하는 FND 모듈의 칩은 Shenzhen Titan Micro Elec - TM74HC595 제품으로 CPOL가 HIGH입니다.

아직 지식이 부족하여 CPHA는 분석하지 못했습니다.

위 그림은 개발보드와 FND 모듈의 CPOL과 CPHA에 설정에 따라 발생하는 상황을 나타낸 그림입니다. FND 모듈에서 데이터를 읽기 시작하는 시점을 점선으로 표시했습니다.

Nexperia-74HC595D 칩은 CPOL이 LOW이기 때문에 개발보드에 CPOL을 HIGH로 설정해도 CPHA가 2 Edge라면 데이터가 누락이 없지만, 1 Edge인 경우 비트 누락이 발생하는 것을 볼 수 있습니다. 그렇기 때문에 CPOL이 HIGH이고 CPHA가 1 Edge인 경우에만 출력값에 오류가 있었던 것입니다.

해결: CPOL을 LOW로 변경

결론적으로 제가 가지고 있는 FND 모듈을 올바르게 제어하려면 CPOL을 LOW로 설정하고, CPHA는 1 Edge로 설정해야한다는 것을 알았습니다. 하지만 CPOL을 HIGH, CPHA를 2 Edge로 설정해도 데이터가 정상적으로 출력되는 것은 개발보드와 FND 모듈이 둘 다 상승 엣지에서 데이터를 확인하기 때문입니다. 또한 CPOL이 LOW이고 CPHA가 2 Edge인 경우에도 다음 상승 엣지 전까지 데이터가 유지되기 때문에 데이터를 누락없이 수신받을 수 있었습니다.

참고자료

[임베디드 21강] STM32에서는 SPI 기능을 제공한다구!

'embedded' 카테고리의 다른 글

| [임베디드] SSD1306 OLED 모듈 제어 - I2C (1) | 2024.09.02 |

|---|---|

| [임베디드] 74HC595D FND 모듈 제어 - GPIO (4) | 2024.08.07 |

| [임베디드] FT232RL USB 모듈 제어 - UART (0) | 2024.07.29 |